Publications

A collection of my research work.

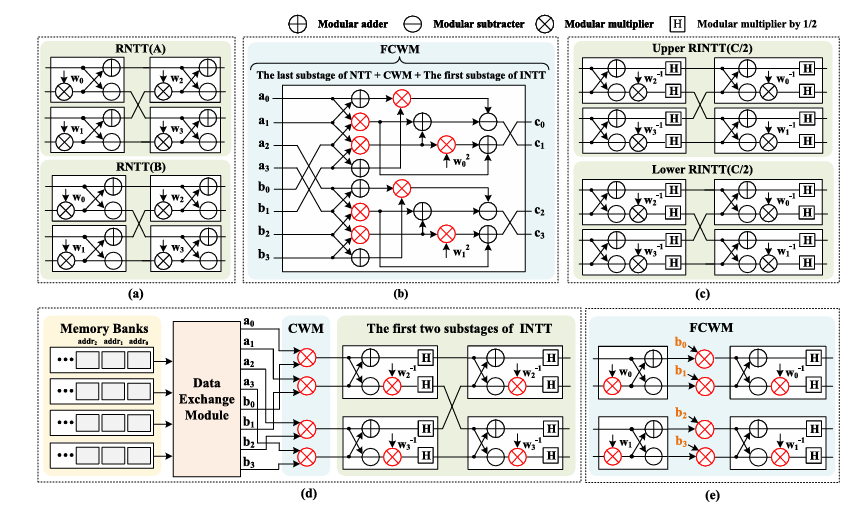

Meta: A Memory-Efficient Tri-Stage Polynomial Multiplication Accelerator Using 2D Coupled-BFUs

Yan Xu, Ling Din, Penggao He, Zhaolun Lu, Jiliang Zhang

IEEE Transactions on Circuits and Systems I: Regular Papers 2025

Built on FPGA, Meta provides specialized hardware acceleration for cryptographic operators, with optimized support for NIST-standardized post-quantum algorithms.

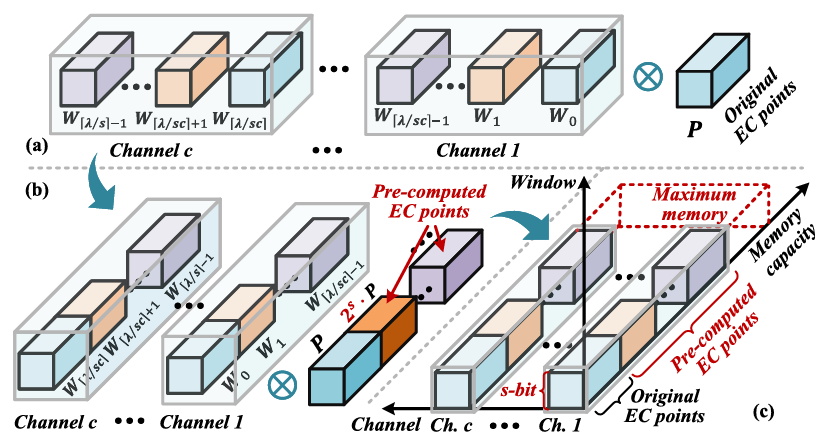

Fama: An FPGA-Oriented Multi-Scalar Multiplication Accelerator Optimized via Algorithm-Hardware Co-Design

Yan Xu, Jinqi Zhang, Xiyan Dong, An Wang, Xinghua Wang, Liehuang Zhu

IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems 2025

FAMA is an FPGA-oriented accelerator for Multi-Scalar Multiplication (MSM), a key bottleneck in zero-knowledge proofs, achieving over 184× speedup over CPUs and superior efficiency over other FPGA designs through algorithm-hardware co-design.